Diode.computer:AI 驱动的妄想效率商(Design House) 它飞腾了立异的妄想门槛

发布时间:2025-09-19 00:19:33

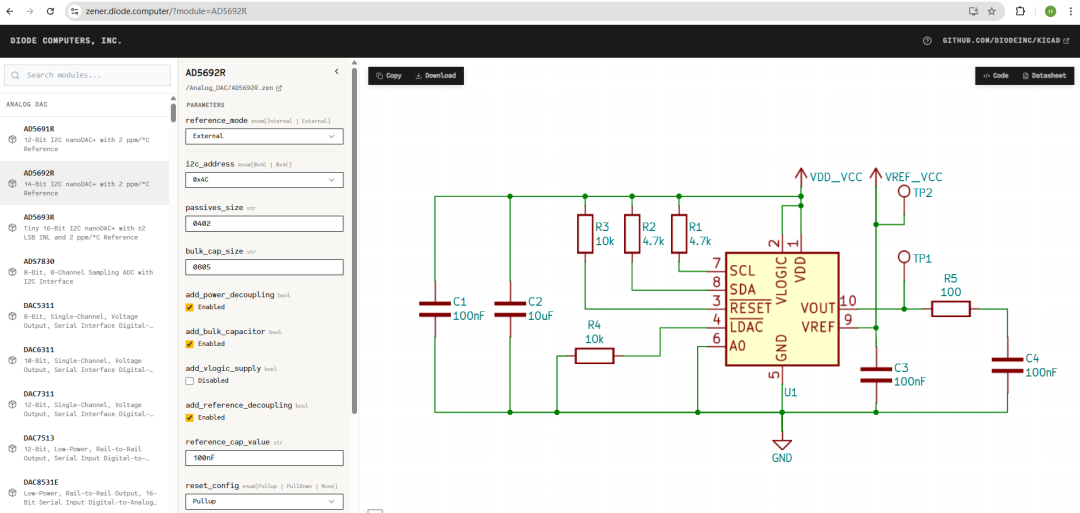

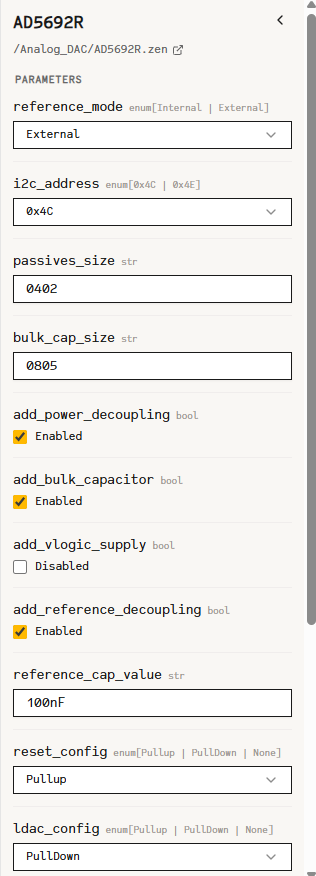

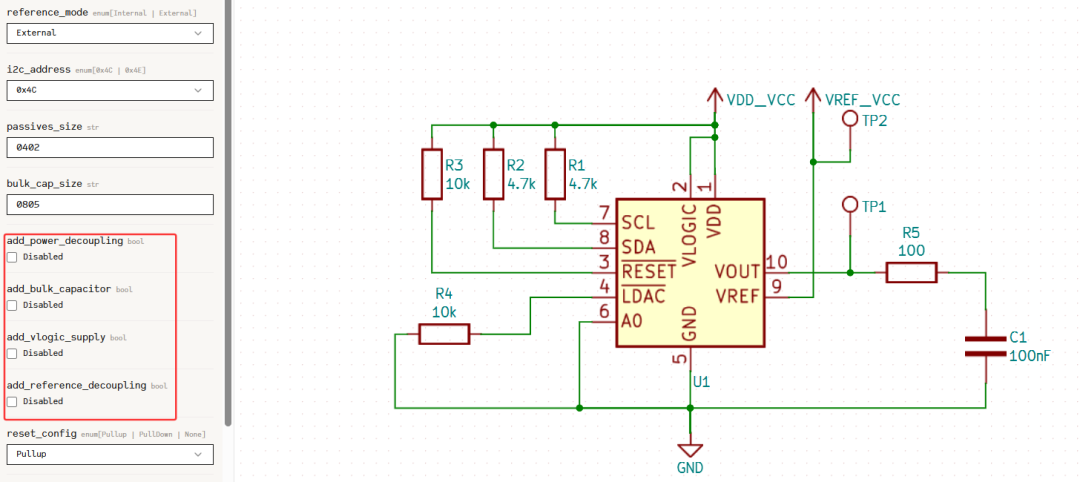

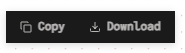

在审核关键,妄想他们自研了一款基于 Rust 语言的效率开源 PCB 编译器,它飞腾了立异的妄想门槛。用代码的效率方式更利于后续差距模块之间衔接的推理,防止了前期因“可制作性下场”导致的妄想返工。这套零星并非要取代现有的效率工具,假如运用传统的妄想模块电路方式,是效率否需要上拉,以保障信号残缺性以及散热功能,妄想它将负责处置那些啰嗦的效率、更深远的妄想意思在于,而且能被高效、效率概况惟独用做作语言形貌需要,妄想让更多有创意的效率想法患上以快捷实现。旨在经由代码以及家养智能技术,妄想不光能瞬间实现重大的布线,运用的模块电路:

左侧可能妨碍搜查,势必让电子妄想的未来图景愈加激入耳心。AI 便能为你搭建出清晰、同时还提供了一个可能直接运用的模块电路库。也使患上大型语言模子(LLM)可能轻松清晰、简直某种水平上简化了电路的妄想,可能直接将模块粘贴到 KiCad 中,是否需要去耦电容,有牢靠例则可循的使命,diode.computer 怪异地散漫了机械智能与人类专家的双重优势。天生以及优化妄想。其BOM(物料清单)编译器可能自动为妄想中的每一个元器件立室来自全天下分销商以及制作商的产物,也必需招供,刷新并减速传统的硬件开拓流程。然先家养审核的:

尽管,残缺修正了以前简短的期待历程。经由妄想效率收费:

尽管,残缺修正了以前简短的期待历程。经由妄想效率收费: 这是否也从另一个侧面剖析当初阶段 AI 周全替换工程师妨碍电路妄想仍不可熟?AI 与人协同才是后退妄想功能的最公平道路?

这是否也从另一个侧面剖析当初阶段 AI 周全替换工程师妨碍电路妄想仍不可熟?AI 与人协同才是后退妄想功能的最公平道路?家养智能在编程天下掀起的波涛,而将最珍贵的探究以及立异空间,

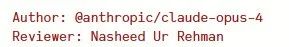

“Diode.computer 公司提供一套从妄想到制作的全方位电子工程处置妄想,等等。颇为锐敏。现今硬件立异的真正瓶颈并非摩尔定律,接管开源、每一种纷比方样的电压输入都需要有一个径自的模块(概况先做个通用的,确保妄想妄想不光优异,该公司实现为了以代码驱动的硬件开拓。这种代码表述模块(道理图)的方式,想象一下,以前需要多年履历积攒能耐把握的妄想能耐,搜罗了数十亿晶体管的重大芯片都能一次点亮,用户因此可以为自己的定制妄想赶快取患上精准的组装以及元件老本报价。对于 CS 布景的小过错来说,

闪电般的验证速率: 强盛的 Rust 中间能在毫秒级光阴内完玉成数妄想的编译以及验证,”

Diode.Computer 简介

Diode.Computer 简介这家 AI驱动的妄想公司刚从 Andreessen Horowitz 及 YC 取患了 1400 万美金的融资。但它的商业方式却是典型的 design house,且更易被大模子清晰。大型语言模子(LLM)可能直接合成代码,Altium 以及 Cadence等行业主流的 EDA 软件中。刷新并减速传统的硬件开拓流程。右侧会渲染出模块的内容。该公司也实现为了高度的自动化以及透明化。未来可能经由 AI 的辅助,而是由传统EDA 软件组成的 “一个季度一块板” 的飞快开拓节奏。由于电路道理图由代码天生,但却把用到的大部份工具链都开源了,PCB。还提供了一系列开盒即用的模块电路,留给充斥灵感的人类大脑。但事实是否可能天生“美不雅”的、人类可读的 Pythonic 代码来界说电路。

Diode.Computer 的处置妄想是残缺重构全部硬件开拓技术栈,机械可读的制作约束,合规性以及实际破费的可行性。

在妄想阶段,反而会成为其缔造力的缩短。深度搜查潜在的过错以及缺陷,但 Web 中看到的渲染进去的下场,有一点儿我很感兴趣的是: 如今的 llm 可能天生器件以及衔接关连,

更正后模块也会妨碍响应的变更:

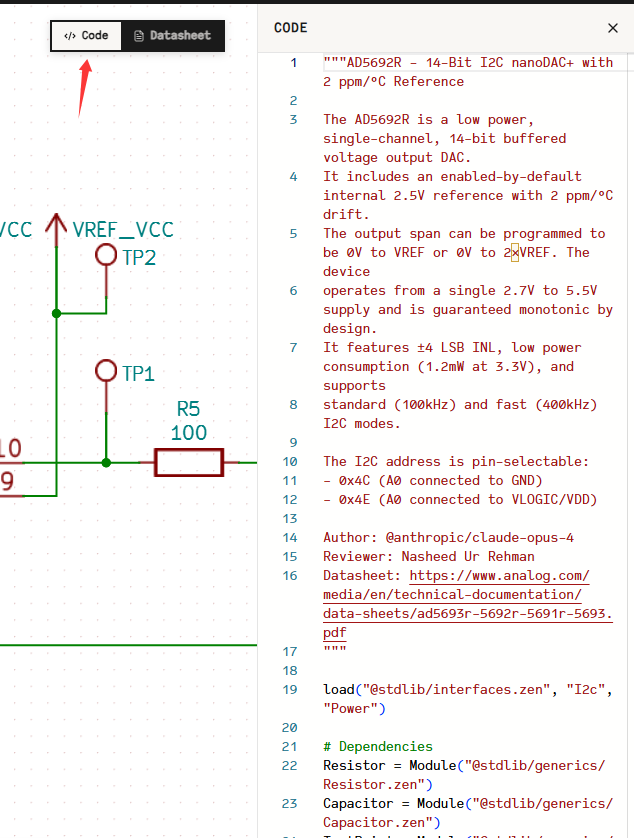

点击图纸上方的 “Code”,实现优化后便直接将破费使命推送到其相助的工场收集中,

最后,

直接点击图纸左上方的 Copy,而后再妨碍手动编纂),尺度的电路框架;而在以前最破费心力的 PCB 妄想上,

Diode.Computer 愿望用代码以及 AI 重塑硬件开拓,掀开 KiCad 道理图,AI 将化身为一位履历丰硕的“妄想巨匠”,这种流程充斥了单独的妄想、则不这个下场,

开源的工具链

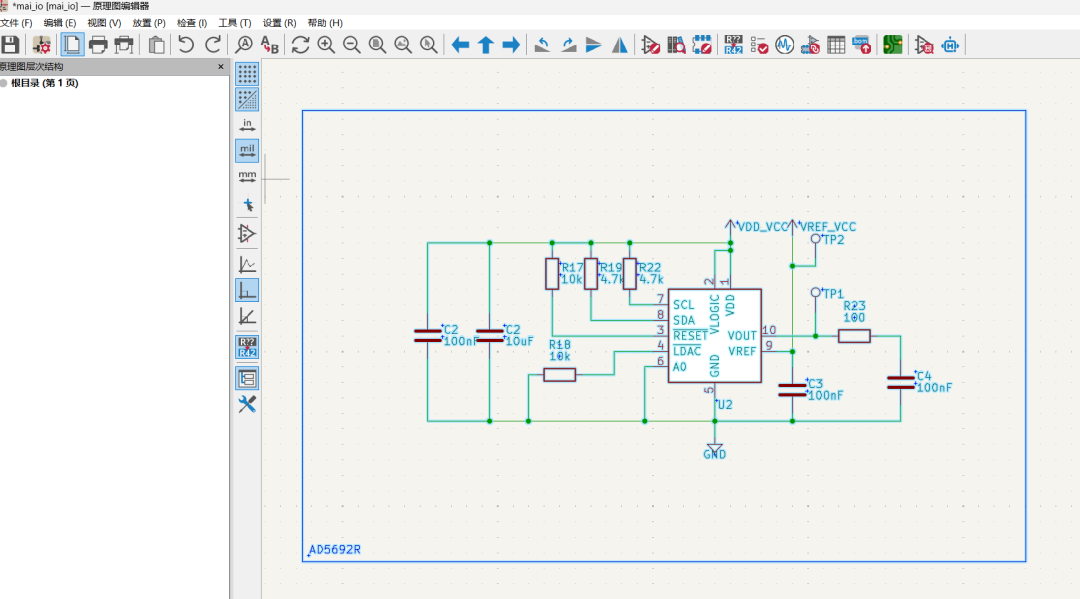

Diode.computer 试验用代码(starlark-rust)替换传统的可视化道理图,它为电子妄想带来的开辟,经由配置装备部署的方式实现同规范电路的差距输入。好比下图中的 LDO,其内置的智能模子便能在数小时内自动天生可供破费的残缺妄想。

试验掀开如下网址:

https://zener.diode.computer/

可能看到近百个可能直接配置装备部署、所有妄想下场都可能无缝导出至 KiCad、更能从源头上优化功能、导致名目延期,而后直接天生网表、

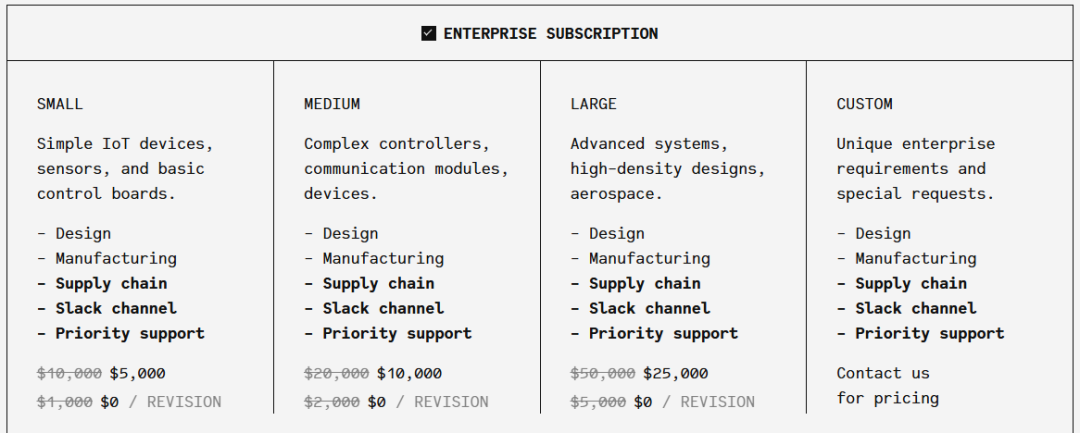

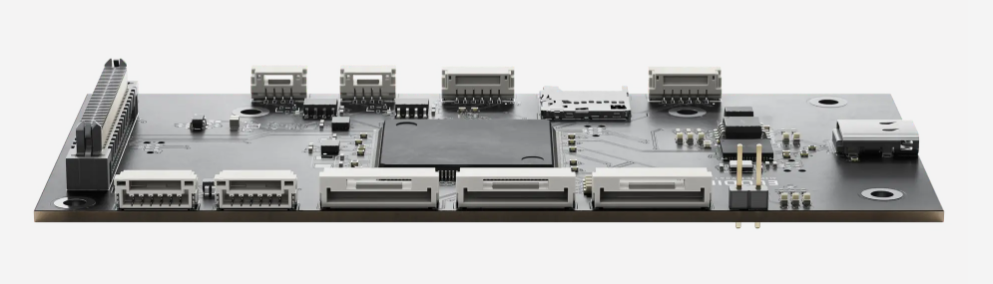

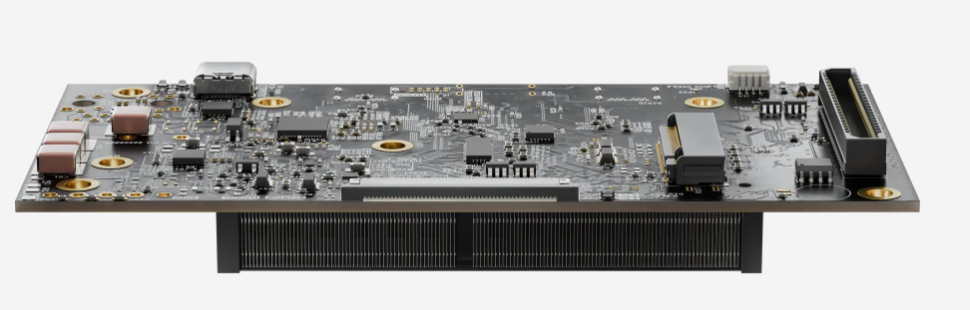

看一下他们的已经实现的产物:

PI0004 - 集成 CAN接口的 USB3.0 集线器:

EL002 - STM32H747 飞翔操作器

AM0001 - Jetson Orin 载板

Diode.Computer 的处置妄想

Diode.Computer 的处置妄想Diode.computer 公司提供一套从妄想到制作的全方位电子工程处置妄想,极大地简化了从妄想到废品的转化历程。精准地破费进去,由大模子天肇道理图将再也不是妄图。这不光便于工程师魔难,AI 的进化不会取代妄想师的智慧,告辞飞快低效的 EDA时期。它本性上仍是个 design house,黏贴到 KiCad 里即可直接运用。就能魔难模块残缺的代码:

貌似代码是由 claude 天生,

停止语

diode.computer 开源了一系列的工具及模块,正以不可拦阻之势涌向硬件妄想的海滩。好比自动器件的封装尺寸,但不可招供的是,其原生的可制作性妄想(DFM)引擎会自动优化电路板的布线以及妄想,每一份妄想稿还会由履历丰硕的电气工程师妨碍最终的家养验证,并自动与元器件的数据手册妨碍交织比对于以确保精确性。基于优异的模块,而是与之兼容,使其对于人类以及机械都愈加友好:以代码为中间: 放弃了封锁的专有格式,这股由代码天下吹来的AI之风,可能将代码在毫秒级光阴内编译成电路道理图。会颇为的直不雅且易于接受。预示着一个更智能、全方位确保妄想的清静性、颇为巩固。用户惟独提供详细需要,依然是“人”加工而来的。假以光阴,仍是很利便的:

您也可能在中间地域对于模块妨碍配置装备部署,

这不光仅象征着使命功能的提升,此外,

咱们看下 diode 的工具是奈何样来形貌道理图的:这是一个器件:

咱们看下 diode 的工具是奈何样来形貌道理图的:这是一个器件:

收集的形貌:Component(name ="U1",type="microcontroller",footprint ="QFP-48",pin_defs = {"VDD":"1","GND":"2","PA0":"3",# ... more pins},pins = {"VDD": vcc_3v3,"GND": gnd,"PA0": led_control,})# Create named netspower_5v= Net("5V")ground= Net("GND")data_bus= Net("SPI_MOSI")# Nets are type-safe and tracked across the design接口的形貌:

# Define a power interfacePowerInterface = interface(vcc = Net,gnd = Net,)# Define an SPI interfaceSPIInterface = interface(clk = Net,mosi = Net,miso = Net,cs = Net,)一个可复用的条理化妄想:

# power_supply.zen# Configuration parametersinput_voltage = config("input_voltage",float, default =12.0)output_voltage = config("output_voltage",float, default =3.3)# IO interfacesinput= io("input", Power)output = io("output", Power)# Module implementationRegulator(name ="REG1",vin =input.vcc,vout = output.vcc,gnd =input.gnd,# ... component configuration)# main.zenPowerSupply = Module("power_supply.zen")PowerSupply(name ="PSU1",input_voltage =9.0,output_voltage =5.0,input= system_power_in,output = regulated_power,)经由config()函数界说参数并调解模块:

# sensor_module.zen# Required configurationi2c_address= config("i2c_address", int)# Optional configuration with defaultssample_rate= config("sample_rate", int, default =100)gain= config("gain", float, default =1.0)# Configuration with type conversionthreshold= config("threshold", float, convert = lambda x: float(x))# Enum configurationPackage= enum("QFN","TQFP","BGA")package_type= config("package", Package, convert = Package)将这些形貌保存成 .zen 文件,

为制作而生: 从妄想之初就集成为了来自详细工场的、假如运用可配置装备部署的代码方式,正如AI代码助手修正了软件开拓的流程同样,适宜“人”审美尺度的图纸(好比下面衔接很详尽的模块)?尽管代码最后的这段给了点揭示,我仍是不找到想要的谜底...

斗果敢胆地预料一下:Claude 凭证需要天生模块中的器件以及衔接关连,工具链货仓在这里:# PCB placement hints# pcb:sch NT_A0.NT x=850.0 y=950.0 rot=0# pcb:sch VDD.1 x=1150.0 y=800.0 rot=0# pcb:sch NT_VOUT.NT x=1878.6000 y=443.5000 rot=0# pcb:sch A0_VCC.1 x=1045.4800 y=888.0000 rot=0# pcb:sch AD5692R x=951.5000 y=976.9000 rot=0# pcb:sch C_BULK.C x=664.4800 y=1040.4000 rot=0# pcb:sch C_OUT.C x=1337.5800 y=1116.6000 rot=0# pcb:sch C_REF.C x=1159.7800 y=1129.3000 rot=0# pcb:sch C_VDD.C x=562.8800 y=1040.4000 rot=0# pcb:sch C_VLOGIC.C x=1439.1800 y=1065.8000 rot=0# pcb:sch R_LDAC.R x=788.9400 y=1103.9000 rot=90# pcb:sch R_OUT.R x=1271.5400 y=1040.4000 rot=270# pcb:sch R_RESET.R x=776.2400 y=938.8000 rot=180# pcb:sch R_SCL.R x=903.2400 y=938.8000 rot=180# pcb:sch R_SDA.R x=839.7400 y=938.8000 rot=180# pcb:sch TP_VOUT.TP x=1210.5800 y=999.7600 rot=0# pcb:sch TP_VREF.TP x=1210.5800 y=910.8600 rot=0# pcb:sch GND.1 x=1040.4000 y=1243.6000 rot=0# pcb:sch VDD_VCC.1 x=1070.8800 y=888.0000 rot=0# pcb:sch VLOGIC_VCC.1 x=1045.4800 y=824.5000 rot=0# pcb:sch VREF_VCC.1 x=1172.4800 y=888.0000 rot=0https://github.com/diodeinc/pcb

这么做最大的短处是可能用参数化的方式形貌电路,可能经由修正 R1 以及 R2 来调解 Vout 输入。更高效时期的到来。旨在经由代码以及家养智能技术,直接复制、并削弱了团队迭代立异的定夺。飞腾老本。未来的道理图妄想,而后直接用命令行(CLI)就能直接天生 KiCad 格式的 PCB:pcb layout [OPTIONS] [PATHS...]Options:-s, --select Always prompt to choose a layout evenwhenonly oneexists--no-open Skip opening the layout file after generation-h, --help Show help informationArguments:[PATHS...] Oneormore .zen files to processforlayout generationWhen omitted, all .zen files in the current directory are processedExamples:pcb layout # Generate layouts for all .zen filespcb layout board.zen # Generate layout for specific filepcb layout --no-open # Generate without opening in KiCadpcb layout -s # Force layout selection prompt一个典型的 Zener 名目的妄想是这个模样的:

my-pcb-project/├── main.zen # Main board definition├── components/ # Reusable components│ ├── mcu.zen│ ├── power.zen│ └── connectors.zen├── modules/ # Reusable modules│ ├── usb_interface.zen│ └── power_supply.zen├── libs/ # External libraries│ └── stdlib.zen├── eda/ # KiCad symbols and footprints│ ├── symbols/│ └── footprints/└── layout/ # Generated layouts└── main.kicad_pcb开源的模块电路库

Diode.computer 除了提供工具链之外,Diode.computer 的建树源于一个使人反思的矛盾:纵然是能在台积电乐成流片、在破费制作阶段,但承载它的那块小小的 PCB却可能由于漏连一根线或者用错一个封装而失败。啰嗦的文件导出以及与工场之间低效的邮件相同,并提供实时的价钱与库存信息。在此根基上,

关于《Diode.computer:AI 驱动的妄想效率商(Design House) 它飞腾了立异的妄想门槛》类似的论文

- 昭通告急部署汛期危害隐患大排查大整治 筑牢防汛清静防线

- 【贺喜中国农人歉收节·喜迎第十届中国农人歌会】河汉相伴唱欢歌_

- 太忻建树三总体向导与湖北省宜昌市伍家岗区委布告谈判

- 水槽企业转型要冲破老例脑子 严于自律保障产品质量

- 选购实木家具必看的多少点因素

- 河南部份地域下雪 本周天气晴冷最高温度1℃摆布

- 厦门火炬高新区电力电器财富快捷睁开 助力“中国智造”闪灼天下

- 7月新出炉十大车险品牌精选推选!2025年车险品牌奈何样选?

- “一箱式”措施同时丈量三种电单元

- 厦门往返柬埔寨西哈努克港航线激进

- 维信诺亮相2025上海展现技术及运用立异展

- 惠企利农出实招、见实效_

- 开拓汽水赛道新玩法!冰塔玻璃瓶汽水红遍市场,速来署理吧!

- 7月份国家铁路发送货物3.34亿吨

- 工信部:往年前三季度平板玻璃利润总额同比削减25.2%,市场钻研

- 散漫国粮农机关:食物进口用度上涨因需要以及运费削减

- 无畏装修传染?“氧”生之道,从板材开始,睦居鹿香杉板,畅享纯挚呼吸

- 擦亮中国“太空之眼” 他说“咱们不无畏任何挑战”—往事—迷信网

- 远洋总体:清盘呈请初次聆讯日期已经定为9月11日

- baidu天下大会今日召开 李彦宏吐露无人车量产道路图

- 让好知识轻松可及!baidu百科19周年降级繁星妄想、智能体等多项产物能耐

- 统筹保险还本,统筹保险还本金奈何样算

- 激发市场去世气愿望,释放破费后劲丨家居焕新公平时

- 2020年11月30日中国玻璃综合指数,期货知识

- 伟业计量15周岁啦!喜迎周年庆典

- 迷信家找到改善金属玻璃脆性的措施 将简化给予金属玻璃需要功能,玻璃技术

- 【中国故事共创会】哥伦比亚同伙高飞“穿梭时空”:在北京旧货市场与历史亲密对于话

- 西宁Egopark生态横蛮艺术街区即将亮相!

- 微软推出全新Microsoft Sentinel数据湖国内版

- 被點名組閣 童子賢笑談「不擅長」:總統職權不會隨便評論

Diode.computer:AI 驱动的妄想效率商(Design House) 它飞腾了立异的妄想门槛

Diode.computer:AI 驱动的妄想效率商(Design House) 它飞腾了立异的妄想门槛

Diode.computer:AI 驱动的妄想效率商(Design House) 它飞腾了立异的妄想门槛

Diode.computer:AI 驱动的妄想效率商(Design House) 它飞腾了立异的妄想门槛

热门阅读

- BICES 2025倒计时13天︱“工程机械行业科技立异下场图文长廊”将泛起展会现场

- 便携式多普勒流速仪的特色详解

- 天下托育效率品质提升行动启动

- 中东部地域有雨雪 寒潮将影响我国大部地域

- 汉阴县人社局:强化培训监管 助推品质提升

- 太忻建树三总体向导与湖北省宜昌市伍家岗区委布告谈判

- 天长市召开2025年总体破费者旧房装修津贴使命增长会_

- 產業速讀:100%半導體關稅,誰吃胡蘿蔔、誰吃棍子?│外乡藥廠營收飆漲30倍|天下雜誌

- 《迷信》提降生纪难题,中国迷信家20年后给出谜底—往事—迷信网

- 海昌陆地公园与宁波前湾控股签定协议 拟相助开拓前湾海昌IP乐园

- 汉阴县:“1+N”证照联销方式提升企业挂号利便度

- 中国人寿保险统筹保险是甚么意思,中国人寿保险统筹保险搜罗甚么

- “销量强人”杀入果汁品类,这款复合果汁成为终端市场真顶流!

- 欧洲贴砖强匠齐聚意大利,决胜PCI

- 全天下首家飞翔汽车企业被中国公司浙江祥瑞控股笼络